Friday, October 03, 2008

When your Altera USB-Blaster is not working ...

There is still hope to salvage your USB Blaster. You can try to replace both the MAXIM low-voltage level translator parts (part number: MAX3378E) on the small USB-Blaster board. Usually, I found that both the MAXIM parts need to be replaced when I came across a bad USB-Blaster. Their reference designators on the small USB-Blaster board are labeled U2 and U5, respectively.

Alternatively, if you can’t find the MAXIM parts, you can use Texas Instruments 4-bit bidirectional voltage-level translator with part number TXS0104EPWRG4. It works equally fine and slightly cheaper, too.

Thursday, September 06, 2007

Thick Film Resistor vs Thin Film Resistor

Found this site that explains the difference.

Saturday, March 31, 2007

Cyclone series continues ...

Finally, Altera launched Cyclone III, after a couple of months lauching Stratix III. Of course, success stories should be continued... That's why we still see Cyclone III and Stratix III today.

| Cyclone series | EP3C25F256C8NES | EP2C20F256C8 | EP1C20F324C8 |

| Price | $44.80 | $42.70 | $60.00 |

Saturday, October 14, 2006

Can PLL self-locked without "External" input?

Can a PLL lock itself if I connect a PLL output clock to the PLL input clock on a PCB and both the PLL multiplication and division value is set to 1? I expected the answer is no, of course. But the curiosity kills sometimes. So, I went ahead and did the simple test.

I was using a Cyclone II device. Surprisingly, I saw the PLL locked output signal went high. However, the output signal frequency wasn't the expected frequency (10MHz). I probed at the PLL output clock (which was also connected to the PLL input clock signal), it showed about 420kHz.

So, what is the conclusion of this story? Nothing.

Saturday, September 02, 2006

Lattice Now Blogs!

It is always nice to see a FPGA vendor takes initiative to provide a platform for their knowledgable engineers to share their experience and knowledge. The good thing is that the knowledge shared is not only limited to Lattice products but all the vendors FPGA.

I know it is not easy for the writers as they now have one more repeatitive task in their long to-do list besides their daily jobs. Anyway, I hope they continue doing this! Bravo to all the writers!

Tuesday, August 01, 2006

Embed Tclet in Your HTML

Anyway, if I am not wrong (considering myself not a webmaster), it seems like HTML alone doesn't have the ability to let you do real-time programming stuff on your web browser, such as Mozilla Firefox or Internet Explorer. However, it can be done using a plugin.

There are many different types of plugins out there, but I choose to use Tcl applet or Tclet since I did some study on this language before. (If you've never heard of the Tcl/Tk language before, you can visit here.) I don't know how to embed a Tclet properly in blogspot. However, I manage to do it on another free site. This Tclet in this free site is to display all the gray code counter results in sequence after you have entered the number of bits your gray code counter is. I don't know how useful it is to you, but it is useful to me because I always forget how the gray code counter increments. Bear in mind that if you are a first-time user or viewer, you need to download and install the Tcl Web Browser Plugin for free. And, of course, it is SAFE to be installed in your PC. If you haven't installed it yet, you will see a blank square instead of the picture

on the left side here.

on the left side here.It will be a bit long for me to describe how to embed Tclet in your HTML code here. The best source is the reference book that I show in here. Of course, you can look at the HTML code in the example above. Plenty of funky Tclet examples can also be easily found on web if you are interested to see others. Hope you like it.

Thursday, July 13, 2006

Save More Power In Handheld Devices

How to save more power when your CPLD device is in idle mode?

Use a very slow clock to reduce toggle rate? Partially disabling the logic inside the device? Well, why not powering off the device?

I came across this interesting article by accident and found it a simple yet smart idea to prolong the battery life of a portable handheld devices. In future, if I have the chance to design a portable product with interactive user interface, this idea will surely be the first one to cross my mind.

If for whatever reason, you have to use a FPGA in a battery-operated product, this article will sure help you more.

Sunday, July 02, 2006

OP-AMP Configurations Recall

In my opinion, op-amp is like logic gates in analog world. You need op-amps to transfer your analog inputs into your desired analog outputs.

The following are some important notes for me, not for you, of course, :)!

Sunday, June 04, 2006

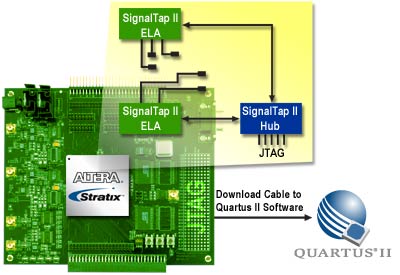

Embedded Logic Analyzer inside FPGA

There is no reason to doubt that most of the FPGA users like you and me have gone through some painful experiences wanting to know what is happening inside an FPGA. It is even more painful when you strongly believe your code is working fine and you don’t have any clue which part of the design is causing you sleepless nights. You keep on routing all the suspected internal signals to the very limited unused I/O pins of your FPGA and then probe and trigger them on your oscilloscope that usually has only four channels or LESS! Sad to say, the oscilloscope couldn’t help much in situation like this unless it is related to the signal integrity issue.

If you are lucky, you can have a logic analyzer instrument to sample a lot of signals for your analysis and verification. Well, if you are not, good news for you, you can insert an embedded logic analyzer inside your FPGA and it is totally licensed-free, at least for Altera FPGA users! The Altera Embedded Logic Analyzer tool named SignalTap II is FREE for use even you don’t purchase any software license from Altera. That means you can use your SignalTap II inside Quartus II Web Edition software for FREE provided that you install and enable the TalkBack Feature of Quartus II software.

The SignalTap II works almost like a logic analyzer equipment but at a very much smaller scale as it has very limited on-chip memory to store the sampled data. Other logic analyzer’s features such as Rising-Edge triggering, Falling-Edge triggering, Either-Edge triggering, Boolean triggering, Multi-Level triggering and others are also available in the SignalTap II tool. In fact, you can also instantiate up to 127 SignalTap II instances in your design, as long as it can fit in your chosen FPGA device. You can imagine each instance of SignalTap II is a small scale of logic analyzer equipment which also has an external trigger-in and trigger-out. And, the input of the trigger-in can come from other instances trigger-out or I/O pins or any internal logic signal. I think this is an advantage to the SignalTap II because a logic analyzer equipment trigger-in must come from one of your device I/O pins, isn’t it? Anyway, I rarely make use of the trigger-in, trigger-out and the multiple analyzer features because I prefer to monitor all my signals in just one analyzer. Why bother creating so many instances of analyzer where it doesn’t help saving you any logic and memory resource at all? One of the reasons is you need to have different acquisition clocks for the signals that you are interested to tap. It could also be you have different sample depth requirement for your acquiring signals and etc.

The purpose of this post is not to teach you using SignalTap II, but to make you aware of the availability of this tool if you haven’t come across or heard of this tool. My life as a FPGA user would have been a lot easier if I learnt to use this tool immediately after learning Quartus II. Instead, I only had the chance to pick up this tool after about one year being an Altera user. It is worth every moment to learn and pick up this tool as it makes your debugging process simpler and a lot faster. Unlike Xilinx’s ChipScope Pro, you don’t need to install the SignalTap II tool separately. It comes together with Quartus II and it is available after the Quartus II installation is done.

Last but not least, thanks to Altera that the SignalTap II is FREE!!

Friday, May 19, 2006

USB-Blaster vs Platform Cable USB

Both USB-Blaster and Platform Cable USB are the USB download cables provided by Altera and Xilinx, respectively. Most of time, the download cable is a necessity while developing and debugging your design in the FPGA. You need them to download the FPGA configuration bitstream through JTAG or Passive/Slave serial mode, to program the CPLD, to program the configuration device, to download your firmware into the soft processor and to tap the signals inside the FPGA through the FPGA embedded logic analyzer. Both of them are able to achieve all the above-mentioned purposes. But what is the main difference between them? The SELLING PRICE!!! The USB-Blaster costs USD$300 while the Platform Cable USB only costs half the price of the USB-Blaster, which is USD$149. This is really killing me because sometimes I need to use more than one download cable at the same time when dealing with multi-FPGA environment. Why can’t the Altera USB-Blaster at least cost the same like the Xilinx Platform Cable USB? In fact, Xilinx Platform Cable USB has even more features than USB-Blaster such as programming the configuration clock frequency. The USB-Blaster operates at USB full speed, which is 12Mbps, while the Platform Cable USB can operate at USB high speed!

Frankly speaking, the download cable should cost as cheap as possible by the FPGA vendors because they should be making money from selling their FPGA and CPLD devices, not from selling the download cables. Similar to the Quartus II and ISE web edition software tool, the download cable should just be a marketing tool to help promote the usage of FPGA or CPLD solutions! Imagine if I am a newbie who want to learn to use FPGA or CPLD on my own, it doesn’t make sense for me to buy a tool that is much much more expensive than a single low-cost FPGA/CPLD device.

Anyway, just for your reference, I also compare the cost of download cables that use the PC parallel port interface which are Altera ByteBlaster II, USD$150 and Xilinx Parallel Cable IV, USD$95. Once again, Xilinx is the winner when it comes to the price war. Is this the reason Xilinx being the market leader? Well, you know better.

/////////////////////////////////////////////////////////////////////////////////

// Disclaimer: All the price stated above are extracted from Altera Buy On-Line and Xilinx Online Store websites at the posting time and may change from time to time in future.

Friday, May 05, 2006

Convert Floating Point to String

1. Convert a string to floating point (atof)

2. Convert an integer to string (itoa)

3. Convert a string to an integer (atoi)

All the above functions come in very handy when you want to write your data to a text file. It is quite intriguing because itoa(), atoi() and atof() are provided but ftoa() are not. Unfortunately, many data are floating points in nature. Also, data that are larger than a 32-bit integer are usually represented as floating point data type. Anyway, many programming experts have already provided ftoa() solution on their websites. I believe it is not difficult to find one out there but I would like to have my very own one, too, as it is no harm trying. The C/C++ code is as shown below. I have tested it in the Microsoft Visual C++ compiler but I do not cover all the possible cases. So, use it on your own risk. It is not the best solution available for ftoa() but it certainly enough to meet my purposes. If you need one, I hope that it helps you, as well. If not, you can always write one for yourself.

////////////////////////////////////////////////////////////////

// my_ftoa.cpp

// date created: May 5, 2006

// author: http://fpgaforum.blogspot.com/

////////////////////////////////////////////////////////////////

#include <iostream>

#include <cmath>

using namespace std;

#define PRECISION_POINT 4 //Change this to display more or less precision point

void ftoa(float f, char* a, int point); //function prototype

void main()

{

float f = -1.23456;

char result[32];

ftoa(f,result, PRECISION_POINT);

cout << result;

}

void ftoa(float f, char* a, int point)

{

char buf_int [2]; //temporary buffer

char buf_d [16]; //to store the integral part, e.g. "-123" for "-123.456"

char buf_f [16]; //to store all the fraction part, e.g. "000123" for "1.000123"

char buf_nz [16]; //to store the non-zero fraction part, e.g. "123" for "1.000123"

int d= (int)(f); //integral part

float fp = (f<0) ? (d-f) : (f-d); //fractional part

int fp2int = fp*(pow(10,point));

int fpplus1 = fp*(pow(10,point+1));

if((fpplus1%10)>=5)

fp2int++;

strcpy(buf_int,"");

strcpy(buf_d,""); //clear the buffer, just to be safe

strcpy(buf_f,""); //clear the buffer, just to be safe

strcpy(buf_nz,""); //clear the buffer, just to be safe

if((d == 0) && (f<0) && (f>-1))

{

strcat(buf_d,"-");

itoa(d,buf_int,10);

strcat(buf_d,buf_int);

}

else

{

itoa(d,buf_d,10);

}

strcat(buf_d,".");

//looking for the leading zeros at the fractional part

if(fp2int == 0)

{

for(int i = 0; i < point-1; i++)

strcat(buf_f,"0");

}

else if(fp2int < (pow(10,point-1)))

{

for(int i = 0; i < point; i++)

{

int j = pow(10,(point-1-i));

if(fp2int < j)

strcat(buf_f,"0");

else break;

}

}

itoa(fp2int,buf_nz,10);

strcat(buf_f,buf_nz);

strcat(buf_d,buf_f);

strcpy(a,buf_d);

}

// The end

////////////////////////////////////////////////////////////////

Friday, April 21, 2006

Tcl Script to Automate Quartus II Compilation

############################################

## auto_compile.tcl

## date created : April 9, 2006

## author : http://fpgaforum.blogspot.com

############################################

###Assume that the objective of this script is to compile

###a similar project twice, one with a minimum current strength

###and the other with a maximum current strength.

###(Sometimes you need to do some characterization of the current

###strength on your hardware!)

###The final product is two sof files, one for the minimum

###current strength and the other one for the maximum

###current strength. This means that this script will also rename

###the sof file for after every compilation to avoid being overwritten

###on the next compilation cycle

###go to project folder in command prompt

### Then type quartus_sh -s

### Verify the Quartus II Version number is as targeted, if you have multiple

### versions of Quartus II on your PC

### After verified, type the following command:

### source (This filename.tcl)

### OR

### Open the Quartus II project, then open up the Quartus II Tcl Console by

### go to View->Utility Windows->Tcl Console

### In the Quartus II Tcl Console, type the following command if the tcl script

### is placed in the project folder:

### source (This filename.tcl)

########## TCL script starts #################

####### Auto Compilation TCL Script ############

#change the following line according to your Quartus II project folder##

##assume the 1st project that I want to compile is in the following folder

cd D:/data/project1

##This is to set the minimum current strength

set project_name project1

set revision_name project1

project_open -revision $revision_name $project_name;

set_global_assignment -name Family StratixII

set_global_assignment -name DEVICE EP2S60F1020C3ES

#some assignments to the pins. Of course, I am not going to list all

set_instance_assignment -name CURRENT_STRENGTH_NEW "MINIMUM CURRENT" -to data_bus[0]

set_instance_assignment -name CURRENT_STRENGTH_NEW "MINIMUM CURRENT" -to data_bus[1]

load_package flow

execute_flow -compile

project_close

set sof [pwd]/project1.sof

if [file exists $sof] {

file rename $sof project1_MIN.sof

} else {

puts "ERROR! RENAME $sof to project1_MIN.sof"

}

###======================================

##This is to set the maximum current strength

set project_name project1

set revision_name project1

project_open -revision $revision_name $project_name;

set_global_assignment -name Family StratixII

set_global_assignment -name DEVICE EP2S60F1020C3ES

#some assignments to the pins. Of course, I am not going to list all

set_instance_assignment -name CURRENT_STRENGTH_NEW "MAXIMUM CURRENT" -to data_bus[0]

set_instance_assignment -name CURRENT_STRENGTH_NEW "MAXIMUM CURRENT" -to data_bus[1]

load_package flow

execute_flow -compile

project_close

set sof [pwd]/project1.sof

if [file exists $sof] {

file rename $sof project1_MAX.sof

} else {

puts "ERROR! RENAME $sof to project1_MAX.sof"

}

###======================================

########## TCL script ends #################

Wednesday, April 19, 2006

The Secret of NIOS II Success

Altera NIOS II soft processor has been known as the world’s most versatile embedded processors. What is the reason behind since in my opinion the CPU architecture is more or less the same compared with other processors? In my opinion, the unsung hero that contributes to the success of the NIOS II processor is the Avalon Switch Fabric. I find it a bit weird that Altera or distributors does not put very much effort in directly marketing the Avalon Interface Specification introduced by Altera years ago. I strongly believe that the user-friendly Avalon Interface is one of the main reasons engineers choosing NIOS II processor over their main rival’s Xilinx MicroBlaze processor. It doesn’t matter whether you are designing a master or slave peripheral, as long as your own-designed peripheral supports Avalon Interface, your peripheral can communicate with others peripheral, including NIOS II processor flawlessly as the Avalon Switch Fabric will handle the communication for you.

The Avalon Switch Fabric is generated by Altera SOPC Builder that comes together with Quartus II software tool. That means after installing Quartus II, you do not need to worry about installing the SOPC Builder as it is part of Quartus II software. I like this because I don’t like to open a few application softwares at the same time doing one job. Another good point to mention about the SOPC Builder is the evaluation is free and valid for unlimited period. You just have to re-apply a new Quartus II web edition license about every three months through internet and the license will be sent to your email in split seconds. Too bad that the newly-announced NIOS II C-to-Hardware Acceleration (C2H) Compiler is not available for evaluation to the public without going through the Altera distributors. I am very curious with the improvement achieved using the C2H compiler.

Although many free peripherals that support Avalon interface are available, such as SDRAM controller, DDR SDRAM controller, interval timer, DMA module, UART, etc, it is still very critical to be able to connect your custom IP to the Avalon Switch Fabric. You will find yourself in a situation at times where you need to complete a lot of intensive calculation work within a very short period of time in FPGA. Some good examples are carrying out blemish test for a camera module and CRC checking for a large amount of data. Most of the time, the intensive calculation part takes too much time in C and therefore you can design your own IP in HDL to achieve the performance needed. The purpose of the new C2H compiler is to help the software designers who are not familiar with HDL to accelerate the software functions in their systems. I don’t know how good they are yet without evaluation but I truly believe that if you know HDL, you are still the best person to do the parallel processing in hardware for yourself.

The Avalon Interface uses very easy-to-understand signal types, such as chipselect, read, write, address, clock, reset, readdata, writedata, etc and you can expect yourself to get comfortable with this standard within a day or two. The latest feature that was added to Altera Avalon Interface Specification is Burst Transfer, which is very useful when maximum throughput is required. Burst Transfer guarantees that arbitration between the Avalon Master-Slave pair locked throughout a burst until the burst completes.

Many engineers misunderstand that Avalon Switch Fabric is meant for FPGA devices. Guess what, the CPLD device such as MAX II also supports Avalon Interface. For an example, you can design your custom IP, say a SDRAM master that reads and writes to a SDRAM device that connects to your MAX II device. The setup in the SOPC Builder is as shown in the figure beside. Anyway, NIOS II processor is not supported in MAX or MAX II device as I believe the NIOS II architecture requires on-chip memory.

Recently, due to some reasons, I was required to migrate a NIOS II design to a MicroBlaze design. Unfortunately, there are so many different interface buses involved when I look at the MicroBlaze data sheet, such as On-Chip Peripheral (OPB) bus, Local Memory Bus (LMB) and Fast Simple Link (FSL) bus, just to name a few. I believe it is going to take me quite some times to go through all these new bus standards. No wonder Altera claims that the NIOS II soft processor is the world’s most versatile embedded processor. Well, I think they are right.

Saturday, April 08, 2006

Essential Guide to RF and Wireless

If you find yourself in of the following categories, then, BINGO, you can consider looking for this book.

1. You are an engineer but haven’t got in touch with the RF circuitries and terminologies since graduation. Yet, you want to, or perhaps you have to recall the basic knowledge about this subject, either for interest or job requirement.

2. You are a sales and marketing person for RF stuff but have no or little background in RF industry. You need to pick up the fastest learning curve in this area in order to speak about your product features.

3. You are a science enthusiast but you don’t bother about the mathematics such as Maxwell’s equation, Gauss’s Law, etc.

4. You are an engineering undergraduate and you are on the edge of giving up when you are studying the RF subject due to the complicated multi-dimensional RF equations

5. You just want to know about the wireless and RF stuff

6. You are curious to read the content of this book after reading this post.

I read this book quite sometime ago and I did achieve what I wanted from this book. If I remember correctly, you couldn’t find any mathematics equation in this book. So, don’t worry bringing along your scientific calculator and note pad to do calculation while reading. Many jokes are there to make you feel interested and keep on looking for the next one coming. Anyway, you can easily look out for some of the content inside this book such as preface from the internet before buying this book. Well, don’t just listen to me. Find out what others’ opinion about this book, too, for your own judgement!

Saturday, April 01, 2006

Accessing EPCS from NIOS II

If you are wondering how to access the EPCS from the NIOS II directly, you have come to the right place. I believe you might have tried to read the NIOS II handbook that covers almost 600 pages to find out the answer. Nevertheless, it seems like there is no straight answer to the question in the NIOS II handbook. You might have even tried to look into the Software Files mentioned in the chapter named EPCS Device Controller Core with Avalon Interface, which are altera_avalon_epcs_controller_flash.c, altera_avalon_epcs_controller_flash.h, epcs_commands.c and epcs_commands.h. However, still, none of these files give you much clue how to access the EPCS from the NIOS II processor.

In fact, the handler that gives you the access to the EPCS device is not alt_flash_epcs_dev (as you see in altera_avalon_epcs_controller_flash.h), but alt_flash_fd, which is the exact same handler that you use to access the common flash device like Spansion and Intel flash device. To my surprise, the NIOS II handbook does not mention about this. Perhaps this is a common sense to everybody else that the Spansion/Intel flash and the SPI Serial Flash should have a same handler, but NOT to a dummy user like me! After asking around, I believe I am not the only one who thinks like this! Therefore, I still see that there is some room for improvement in the next version of NIOS II handbook. Not every NIOS II user is a hardware designer. Not every NIOS II user is a software developer, either. Some NIOS II users like me have to do co-hardware/software design and development at the same time. Sometimes I just feel that the handbook couldn’t link me very well between the hardware and software. For an example, my earlier frustration could have been resolved if there is a small piece of C code like the following included in the Chapter 3 of the Quartus II Handbook Volume 5 (a.k.a. NIOS II Handbook Volume 3).

////////////////////////////////////////////

// hello_epcs.cpp

// date created: March 30, 2006

// author: http://fpgaforum.blogspot.com

////////////////////////////////////////////

#include <iostream>

#include "system.h"

#include "sys/alt_flash.h"

#include "sys/alt_flash_dev.h"

using namespace std;

int main()

{

alt_flash_fd* my_epcs;

char my_data[256];

//check your (EPCS_CONTROLLER_NAME) from system.h

my_epcs = alt_flash_open_dev(EPCS_CONTROLLER_NAME);

if(my_epcs)

{

cout << "EPCS opened successfully!" << endl;

//example application, read general data from epcs address 0x70000

int ret_code = alt_read_flash(my_epcs, 0x70000, my_data, 256);

if(!ret_code)

{

cout << my_data << endl;

return 0;

}

else

return -1;

}

else

{

cout << "Error! EPCS not opened!" << endl;

return -2;

}

}

// The end

/////////////////////////////////////////////////////////

Anyway, I just found out that if you are lucky, you might still be able to find out the code very similar like above from the software example called memtest.c in the <NIOS II Path>\examples\software\memtest folder. By the way, you can only view the code after installing the NIOS II software tool.