There is no reason to doubt that most of the FPGA users like you and me have gone through some painful experiences wanting to know what is happening inside an FPGA. It is even more painful when you strongly believe your code is working fine and you don’t have any clue which part of the design is causing you sleepless nights. You keep on routing all the suspected internal signals to the very limited unused I/O pins of your FPGA and then probe and trigger them on your oscilloscope that usually has only four channels or LESS! Sad to say, the oscilloscope couldn’t help much in situation like this unless it is related to the signal integrity issue.

If you are lucky, you can have a logic analyzer instrument to sample a lot of signals for your analysis and verification. Well, if you are not, good news for you, you can insert an embedded logic analyzer inside your FPGA and it is totally licensed-free, at least for Altera FPGA users! The Altera Embedded Logic Analyzer tool named SignalTap II is FREE for use even you don’t purchase any software license from Altera. That means you can use your SignalTap II inside Quartus II Web Edition software for FREE provided that you install and enable the TalkBack Feature of Quartus II software.

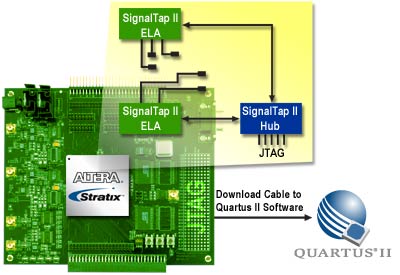

The SignalTap II works almost like a logic analyzer equipment but at a very much smaller scale as it has very limited on-chip memory to store the sampled data. Other logic analyzer’s features such as Rising-Edge triggering, Falling-Edge triggering, Either-Edge triggering, Boolean triggering, Multi-Level triggering and others are also available in the SignalTap II tool. In fact, you can also instantiate up to 127 SignalTap II instances in your design, as long as it can fit in your chosen FPGA device. You can imagine each instance of SignalTap II is a small scale of logic analyzer equipment which also has an external trigger-in and trigger-out. And, the input of the trigger-in can come from other instances trigger-out or I/O pins or any internal logic signal. I think this is an advantage to the SignalTap II because a logic analyzer equipment trigger-in must come from one of your device I/O pins, isn’t it? Anyway, I rarely make use of the trigger-in, trigger-out and the multiple analyzer features because I prefer to monitor all my signals in just one analyzer. Why bother creating so many instances of analyzer where it doesn’t help saving you any logic and memory resource at all? One of the reasons is you need to have different acquisition clocks for the signals that you are interested to tap. It could also be you have different sample depth requirement for your acquiring signals and etc.

The purpose of this post is not to teach you using SignalTap II, but to make you aware of the availability of this tool if you haven’t come across or heard of this tool. My life as a FPGA user would have been a lot easier if I learnt to use this tool immediately after learning Quartus II. Instead, I only had the chance to pick up this tool after about one year being an Altera user. It is worth every moment to learn and pick up this tool as it makes your debugging process simpler and a lot faster. Unlike Xilinx’s ChipScope Pro, you don’t need to install the SignalTap II tool separately. It comes together with Quartus II and it is available after the Quartus II installation is done.

Last but not least, thanks to Altera that the SignalTap II is FREE!!